SubLVDS技术简介

LVDS是一种低摆幅差分信号技术,使用非常低的幅度信号,通过一对差分PCB连线或者平衡电缆传输数据,它可以达到每秒数百兆比特以上的传输速率,而且具有很多优点:恒定的驱动电流、低功耗、简单的PCB板的设计、良好的抗电磁干扰,对于电源、地、外部环境的噪声的不敏感等。在国际标准ANsI/EIA一644中,主要定义了LVDS的电特性,并建议了655 Mbps的最大速率和1.823 Gbps的无失真媒质上的理论极限速度;在IEEE P1596.3中,主要面向SCI(Scalable Coherent Interface),定义了LVDS的电特性,还定义了SCI协议中包交换时的编码。在两个标准中都指定了与物理媒质无关的特性,这保证了LVDS能够成为多用途的接口标准。

SubLVDS(如图1所示)作为LVDS的发展,采用低摆幅电流模式传输系统,同传统的电压模式相比较,在达到几乎相同的性能水平时,由于有比传统模式更好的抗电源噪声能力,它可以在噪声容限低得多,而且摆幅也低得多的情况下工作。设计一个高效电流模式电路的主要挑战是静态功耗,但这在超高速网络中不成问题,因为这时的动态功耗往往起主要作用。再者,此处采用了更加先进的工艺,将供电电压从2.5 V降到1.8 V,输出电压摆幅从350 mV降为150 mV,从而可以达到更低的功耗和提供更高的传输速率。

SubLVDS驱动电路

驱动电路是SubLVDS中的重要部分,其功能是实现将输入的CMOS信号转换为差分输出信号,使得在传输过程中,抗噪特性更好。本研究中的驱动电路主要分为2部分:pre.driver和transmitter。

SubLVDS驱动电路的设计:http://www.elecfans.com/soft/49/52/2010/2010042173735.html

连续脉冲发生器电路图

连续脉冲发生器电路图

时间:2026-03-05

正弦波发生器原理图

正弦波发生器原理图

时间:2026-03-05

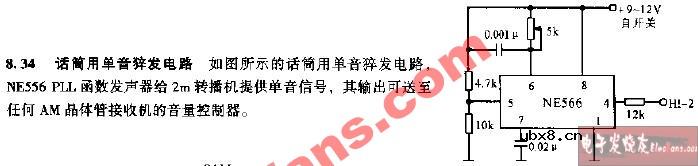

话筒用单音猝发电路

话筒用单音猝发电路

时间:2026-03-05

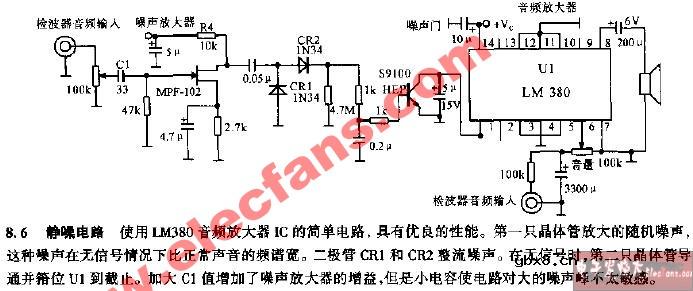

静噪电路图

静噪电路图

时间:2026-03-05

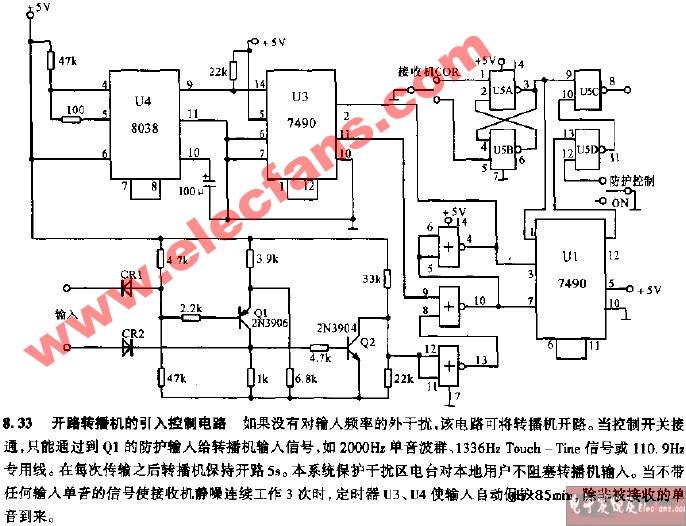

开路转播机的引入控制电路

开路转播机的引入控制电路

时间:2026-03-05

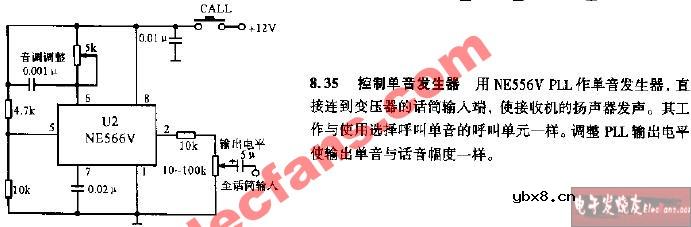

控制单音发生器电路

控制单音发生器电路

时间:2026-03-05

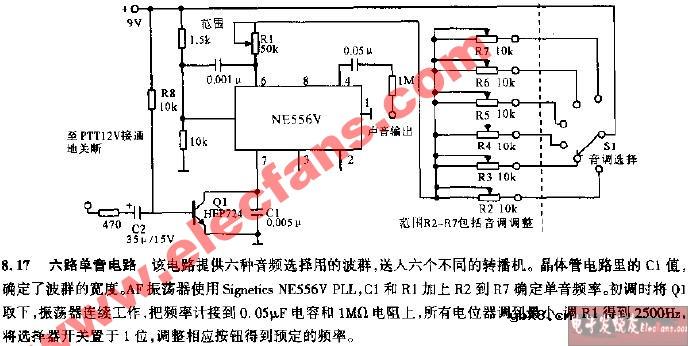

六路单管电路图

六路单管电路图

时间:2026-03-05

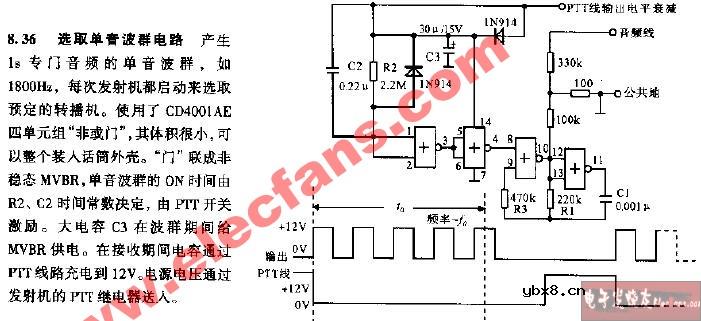

选取单音波群电路

选取单音波群电路

时间:2026-03-05

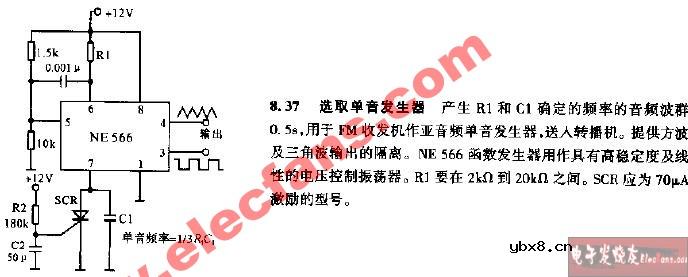

选取单音发生器电路

选取单音发生器电路

时间:2026-03-05

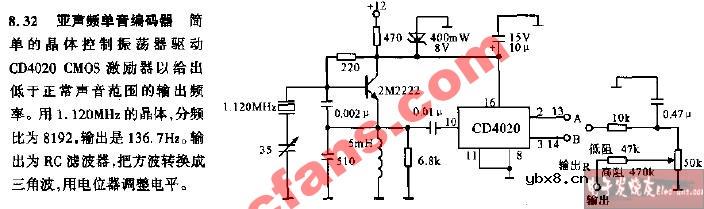

亚声频单音编码器电路

亚声频单音编码器电路

时间:2026-03-05

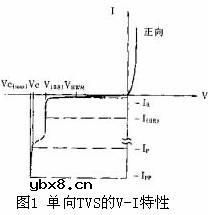

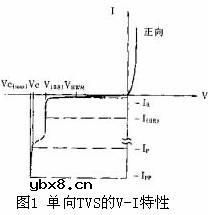

瞬间抑制二极管(TVS)/瞬间抑制二极管(TVS)是...

瞬间抑制二极管(TVS)/瞬间抑制二极管(TVS)是...

时间:2026-03-04

什么是霍尔传感器

什么是霍尔传感器

时间:2026-03-05

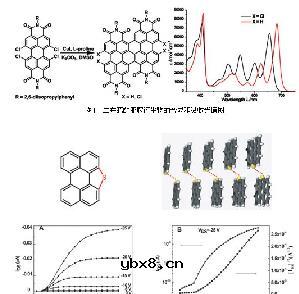

半导体材料的主要种类有哪些?

半导体材料的主要种类有哪些?

时间:2026-03-04

高级封装,高级封装是什么意思

高级封装,高级封装是什么意思

时间:2026-03-04

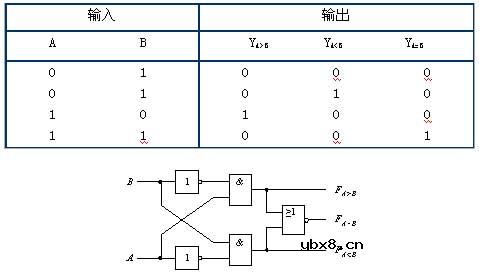

数字比较器,数字比较器是什么意思

数字比较器,数字比较器是什么意思

时间:2026-03-04

常用整流二极管型号大全

常用整流二极管型号大全

时间:2026-03-04

S/HS固态继电器原理简介

S/HS固态继电器原理简介

时间:2026-03-04

稳压二极管的选用和代换

稳压二极管的选用和代换

时间:2026-03-04

TVS器件的电特性有哪些

TVS器件的电特性有哪些

时间:2026-03-04

TVS二极管的分类/应用,TVS二极管的特点/选用...

TVS二极管的分类/应用,TVS二极管的特点/选用...

时间:2026-03-04